东芝记忆体公司开发出全新桥接芯片,利用 PAM 4 提升固态硬盘速度和容量

February 21, 2019

Toshiba Memory Corporation

【东京讯】全球记忆体解决方案领导厂商东芝记忆体公司,今日宣布成功开发可实现高速、大容量固态硬盘的桥接芯片。该公司利用所开发的小型、低耗电量桥接芯片,比传统无桥接芯片使用更少的高速讯号线,成功连接更多快闪记忆体芯片。这项成果已发布于 2 月 20 日在旧金山举行的 2019 年国际固态电路研讨会 (ISSCC 2019)。

在固态硬盘中,多个快闪记忆体芯片需连接至管理运行的控制器。随著越多快闪记忆体芯片连接至控制器界面,运行速度会下降,因此能够连接的芯片数量有限。若要提升容量,就必须增加界面的数量,但这会导致连接至控制器的高速讯号线数量过多,使得固态硬盘电路板的配线变得更加困难。

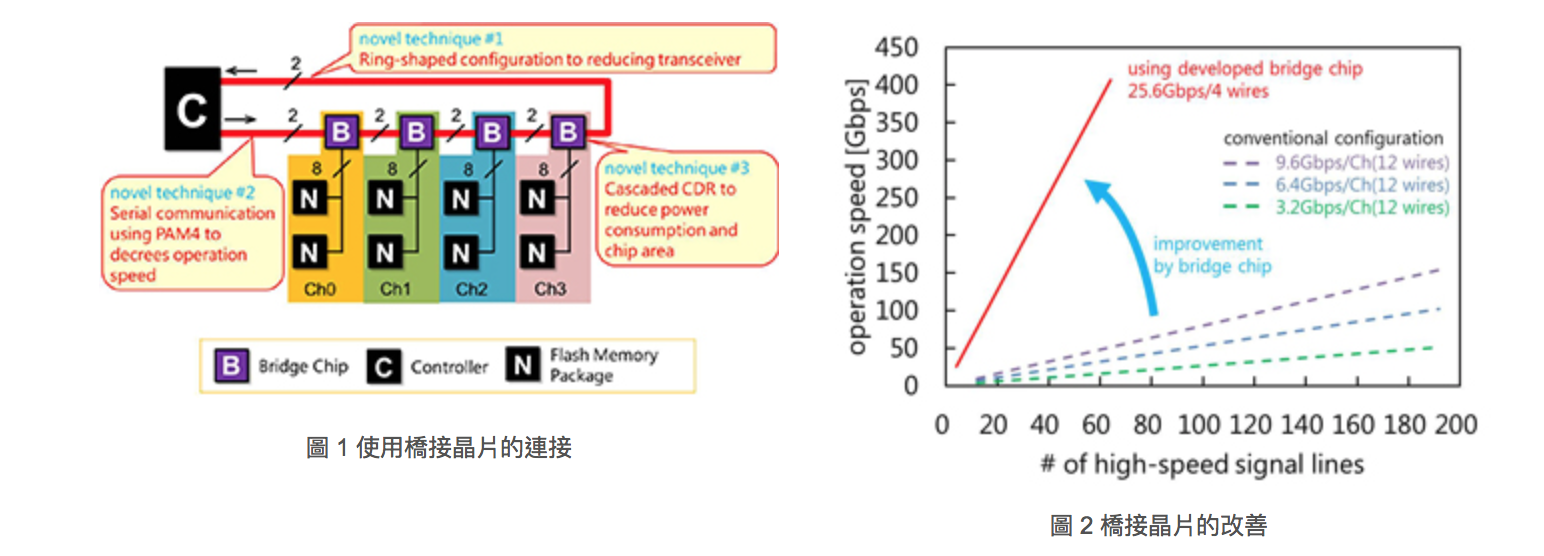

该公司利用可连接控制器和快闪记忆体芯片的桥接芯片 (图 1) 克服了这个问题,其中包含三种新技术:菊链*1 连接,以环状方式连接控制器和桥接芯片;采用 PAM 4*2 的序列通讯;以及抖动 (jitter)*3 改善技术,不再需要在桥接芯片使用 PLL 电路*4。凭借以上技术,能够减少桥接芯片的开销,而且仅需透过几条高速讯号线,就能高速运行大量的快闪记忆体芯片 (图 2)。

桥接芯片和控制器的环状结构,可将桥接芯片需要的收发器数量从两对减少至一对,缩小桥接芯片的面积。此外,在控制器和菊链式桥接芯片之间采用 PAM 4 序列通讯,可降低桥接芯片电路的运行速度和所需效能。全新 CDR*5 可利用 PAM 4 的特性来改善抖动特性,让桥接芯片中不再需要安装 PLL 电路,进而达到减少芯片面积和耗电量的效果。

原型桥接芯片采用 28nm CMOS 制程,并以环状菊链方式连接四个桥接芯片与一个控制器,借此评估成果。经过证实,在 25.6 Gbps 速度下,所有桥接芯片和控制器都拥有良好的 PAM 4 效能,且可达到低于 10-12 的 BER*6。

展望未来,东芝记忆体将进一步加强桥接芯片效能,并减少芯片面积与耗电量,以持续开发前所未见的高速、大容量储存技术。

备注

*1 菊链:将多个芯片按顺序连接的方式

*2 PAM 4:4 级脉幅调变 (包含 4 数值资料)

*3 抖动 (jitter):时脉或讯号波形时域的波动

*4 PLL:锁相回路 (产生准确参考讯号的电路)

*5 CDR:时脉资料回复 (从接收讯号还原资料与时脉的电路)

*6 BER:位元错误率 (数值越低,效能越佳)

- 2019-08-12Toshiba Memory America优化面向SSD的RocksDB

- 2019-08-12东芝存储器株式会社推出XL-FLASH™存储级内存解决方案

- 2019-08-12东芝存储器株式会社在闪存峰会上展示业界最先进企业级应用的[1]PCIe®4.0SSD

- 2019-07-24东芝记忆体将于10月起更名为“铠侠(Kioxia)

- 2011-01-26世平集团推出多重选择的电容式触摸屏平板电脑解决方案